Abstract

Analog-to-digital-conversion enables usage of digital signal processing (DSP) in lots of applications today for example wireless communication, radar and electronic warfare. DSP may be the favored option for processing information over analog signal processing (ASP) since it can typically offer more exibility, computational power, reproducibility, speed and precision when processing and removing information. Software dened radio (SDR) receiver is a obvious illustration of this, where rf waveforms are changed into digital form as near to the antenna as you possibly can and all sorts of processing from the information within the received signal is extracted inside a congurable manner using DSP. To have such goals, the data collected in the real life signals, that are generally analog within their nature, must become digital form prior to it being processed using DSP within the particular systems. The most popular trend during these systems is not only to process ever bigger bandwidths of information but additionally to process data in gifs at ever greater processing speeds with plenty of conversion precision. Therefore the analog-to-digital-ripper tools (ADC), which converts real life analog waveforms into digital form, is among the most significant cornerstones during these systems.

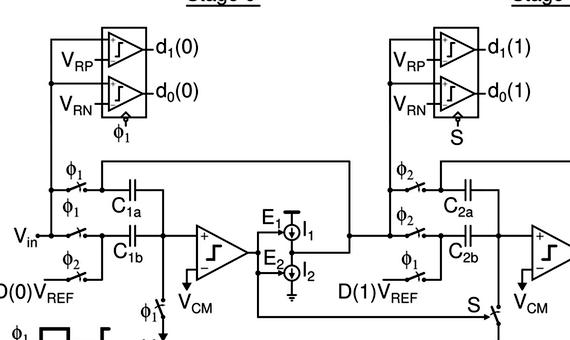

The ADC must perform data conversion at greater and greater rates and digitize ever-growing bandwidths of information. In compliance using the Nyquist-Shannon theorem, the rate of conversion from the ADC should be suffcient to accomodate the BW from the signal to become digitized, to prevent aliasing. The rate of conversion from the ADC can generally be elevated by utilizing parallel ADCs with every ADC performing the sampling at mutually different closing dates.

Interleaving the outputs of each one of the individual ADCs provides a greater digitization output rate. Such ADCs are known as TI-ADC. However, the mismatches between your ADCs cause undesirable spurious artifacts within the TI-ADC’s spectrum, ultimately resulting in a loss of revenue in precision within the TI-ADC when compared to individual ADCs. Therefore, the removal or correction of those undesirable spurious artifacts is important in getting a higher performance TI-ADC system.

To be able to take away the undesirable interleaving artifacts, one that describes the behaviour from the spurious distortion products is extremely important as it can certainly then facilitate the introduction of efficient digital publish-processing schemes. One major contribution of the thesis includes the novel and comprehensive modeling from the spurious interleaving mismatches in numerous TI-ADC scenarios. This novel and comprehensive modeling will be found in developing digital estimation and correction techniques to take away the mismatch caused spurious artifacts within the TI-ADC’s spectrum and recovering its lost precision. Novel and rst available digital estimation and correction methods are developed and tested to suppress the regularity dependent mismatch spurs based in the TI-ADCs. The developed methods, with regards to the estimation from the unknown mismatches, develop record I/Q signal processing concepts, relevant without specically tailored calibration signals or waveforms.

Strategies to boost the analog BW from the ADC will also be examined and novel solutions are presented. The interesting mixture of utilizing I/Q downconversion along with TI-ADC is examined, which not just extends the TI-ADC’s analog BW but additionally provides exibility in being able to access radio stations spectrum. Undesirable spurious components produced throughout the ADC’s bandwidth extension process will also be examined and digital correction methods are designed to remove these spurs in the spectrum. The developed correction approaches for removing the undesired interleaving mismatch artifacts are validated and tested using various HW platforms, with as many as 1 GHz immediate bandwidth. Comprehensive test scenarios are produced using measurement data acquired from HW platforms, which are utilized to make sure assess the performance from the developed interleaving mismatch estimation and correction schemes, evidencing excellent performance in most studied scenarios.

The ndings and results presented within this thesis lead towards growing the analog BW and rate of conversion of ADC systems without losing conversion precision. Overall, these developments pave the way in which towards fullling the continuously growing demands around the ADCs when it comes to greater conversion BW, precision and speed.

Field of science, Statistics Finland

Downloads statistics

No data available

Open Access permissions

Documents

Final printed version, 4 MB, PDF-document

Links

Final printed version

Availability

Authors

Research units

Graph of relations

Tampere College of Technologies are in the innovative of technology development along with a searched for-after collaboration partner one of the scientific and business communities. The College produces competent graduates who enter careers within the different sectors of society.

Health policy phd thesis proposal

Health policy phd thesis proposal Woman point zero thesis proposal

Woman point zero thesis proposal Li shiuan peh phd thesis writing

Li shiuan peh phd thesis writing Human nature essay thesis proposal

Human nature essay thesis proposal University of st andrews library thesis dissertations

University of st andrews library thesis dissertations