A floating-purpose multiplier is certainly not new. The IEEE 754 customary was printed in 1985 and it was mainly according to work which was already recent at that time. Why must engineers spend some time redesigning the proverbial wheel? Quite simply, they ought to not. However they do, regardless. Engineers pay precious style time on already completed tasks for many reasons. Possibly they require a multiplier having a 25-bit significant rather from the quality 12. Possibly they have to squeeze the multiplier onto an area programmable gate array along with other massive parts, and don’t have space to include unneeded options.

All calculations are carried out on double precision figures, if the input operands have been in single precision, they need to be transformed into double precision. Single-To-Double Conversion Block carries conversion task. After double precision values are acquired, two figures are checked for predefined special values that effect can result in determined instantly, if your situation is identified output is generated by special output block. If no situation is located operands are split up into three parts: sign, exponent and mantissa, and each of these is routed to particular arithmetic block. Mantissa Arithmetic Block task would be to multiply 2 53 bit binary figures (most significant bit is assumed to become ‘one’), normalize the end result from multiplier, and round normalized worth. It conjointly generates signals foe exponent road to adjust exponent for normalization and rounding overflow, and inexact signal for special situation output.

For multiplying operation of floating point figures, sign, exponent and mantissa half ought to be handled individually. Because IEEE 754 format (single) of floating point format is adopted here.

Thus, every operand has eight-bit exponent and 23-bit mantissa and something-bit sign. To calculate the end result, the calculation consists of

- Single-bit XOR signs of two operands.

- 8-bit inclusion of the exponents of two operands.

- 12-bit multiplication will be performed to generate the fraction result.

This is actually the fundamental three steps. Some accessories are also needed for shift operation and additional eight bit adder or subtractor to regulate the bias of exponent part in IEEE 754 format.

Rounding occur in floating purpose multiplication once the mantissa from the method is reduced from 48 bits to 24 bits. The most unimportant 24 bits are discarded. Overflow takes place when the add from the exponents exceeds 127, the biggest worth that’s outlined in bias-127 exponent representation. At these times, the exponent is placed to 128 (E = twenty fivefive) and also the mantissa is able to zero indicating + or – infinity. Underflow takes place when the total from the exponents is much more negative than -126, the top negative value that’s defined in bias-127 exponent illustration. When this happens, the exponent is going to -127 (E = zero). If M = zero, the amount is precisely zero. If M isn’t zero, a de-normalized range is indicated with a devotee of -127 along with a hidden bit of . The tiniest such range that is not zero is a set of-149. This range maintains merely a single bit of precision inside the rightmost bit of the mantissa.

- Math coprocessors

- DSP algorithms

- Embedded arithmetic coprocessor

- Information systems control

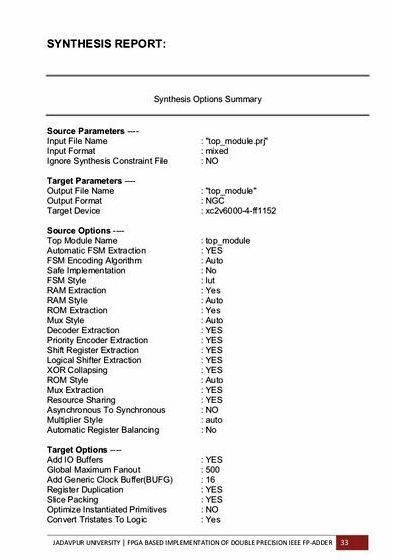

- MODELSIM – Simulation,

- XILINX-ISE – Synthesis

A floating-purpose multiplier is certainly not new.

The IEEE 754 customary was printed in 1985 and it was mainly according to work which was already recent at that time. Why must engineers spend some time redesigning the proverbial wheel? Quite simply, they ought to not. However they do, regardless. Engineers pay precious style time on already completed tasks for many reasons. Possibly they require a multiplier having a 25-bit significant rather from the quality 12. Possibly they have to squeeze the multiplier onto an area programmable gate array along with other massive parts, and don’t have space to include unneeded options.

All calculations are carried out on double precision figures, if the input operands have been in single precision, they need to be transformed into double precision. Single-To-Double Conversion Block carries conversion task. After double precision values are acquired, two figures are checked for predefined special values that effect can result in determined instantly, if your situation is identified output is generated by special output block. If no situation is located operands are split up into three parts: sign, exponent and mantissa, and each of these is routed to particular arithmetic block. Mantissa Arithmetic Block task would be to multiply 2 53 bit binary figures (most significant bit is assumed to become ‘one’), normalize the end result from multiplier, and round normalized worth. It conjointly generates signals foe exponent road to adjust exponent for normalization and rounding overflow, and inexact signal for special situation output.

For multiplying operation of floating point figures, sign, exponent and mantissa half ought to be handled individually. Because IEEE 754 format (single) of floating point format is adopted here. Thus, every operand has eight-bit exponent and 23-bit mantissa and something-bit sign. To calculate the end result, the calculation consists of

- Single-bit XOR signs of two operands.

- 8-bit inclusion of the exponents of two operands.

- 12-bit multiplication will be performed to generate the fraction result.

This is actually the fundamental three steps. Some accessories are also needed for shift operation and additional eight bit adder or subtractor to regulate the bias of exponent part in IEEE 754 format.

Rounding occur in floating purpose multiplication once the mantissa from the method is reduced from 48 bits to 24 bits. The most unimportant 24 bits are discarded. Overflow takes place when the add from the exponents exceeds 127, the biggest worth that’s outlined in bias-127 exponent representation. At these times, the exponent is placed to 128 (E = twenty fivefive) and also the mantissa is able to zero indicating + or – infinity. Underflow takes place when the total from the exponents is much more negative than -126, the top negative value that’s defined in bias-127 exponent illustration. When this happens, the exponent is going to -127 (E = zero). If M = zero, the amount is precisely zero. If M isn’t zero, a de-normalized range is indicated with a devotee of -127 along with a hidden bit of . The tiniest such range that is not zero is a set of-149. This range maintains merely a single bit of precision inside the rightmost bit of the mantissa.

- Math coprocessors

- DSP algorithms

- Embedded arithmetic coprocessor

- Information systems control

- MODELSIM – Simulation,

- XILINX-ISE – Synthesis

Halimbawa ng pamagat para sa thesis proposal

Halimbawa ng pamagat para sa thesis proposal Essay thesis definition in writing

Essay thesis definition in writing Skywire writing with a thesis 11th edition

Skywire writing with a thesis 11th edition Thesis title proposal for tourism

Thesis title proposal for tourism Working at mcdonalds etzioni thesis writing

Working at mcdonalds etzioni thesis writing